- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9910 (Analog Devices, Inc.) 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9910 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的,14位,3.3伏的CMOS直接數字頻率合成 |

| 文件頁數: | 6/60頁 |

| 文件大小: | 764K |

| 代理商: | AD9910 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9910

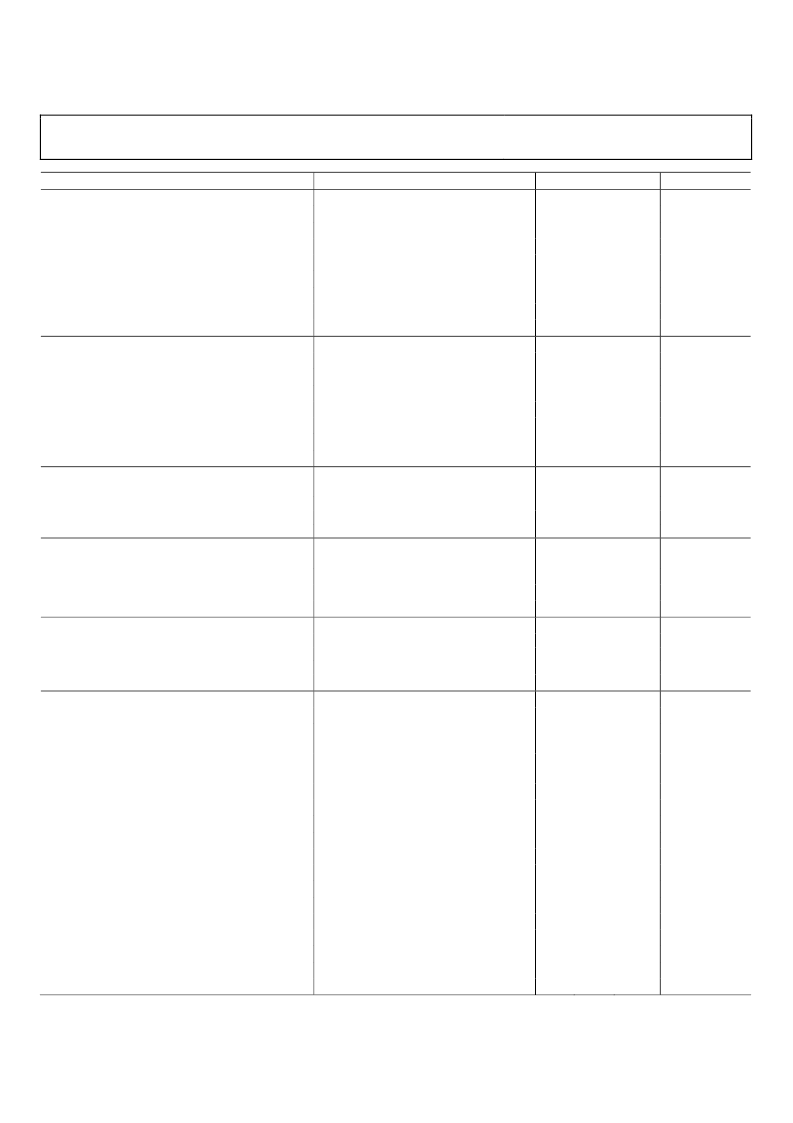

Parameter

201.1 MHz Analog Output

301.1 MHz Analog Output

401.3 MHz Analog Output

SERIAL PORT TIMING CHARACTERISTICS

Maximum SCLK Frequency

Minimum SCLK Clock Pulse Width

Maximum SCLK Rise/Fall Time

Minimum Data Setup Time to SCLK

Minimum Data Hold Time to SCLK

Maximum Data Valid Time in Read Mode

I/O_UPDATE/PS0/PS1/PS2 TIMING

CHARACTERISTICS

Minimum Pulse Width

Minimum Setup Time to SYNC_CLK

Minimum Hold Time to SYNC_CLK

Tx_ENABLE and 16-BIT PARALLEL (DATA) BUS

TIMING

Maximum PDCLK Frequency

Tx_ENABLE/Data Setup Time (to PDCLK)

Tx_ENABLE/Data Hold Time (to PDCLK)

MISCELLANEOUS TIMING CHARACTERISTICS

Wake-Up Time

2

Fast Recovery

Full Sleep Mode

Minimum Reset Pulse Width High

DATA LATENCY (PIPE_LINE DELAY)

Data Latency, Single Tone or using Profiles

Frequency, Phase, Amplitude-to-DAC Output

Rev. 0 | Page 6 of 60

Conditions/Comments

±500 kHz

±125 kHz

±12.5 kHz

±500 kHz

±125 kHz

±12.5 kHz

±500 kHz

±125 kHz

±12.5 kHz

Low

High

Min

Typ

–87

–87

–91

–86

–86

–88

–84

–84

–85

70

2

Max

11

Unit

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

Mbps

ns

ns

ns

ns

ns

ns

4

4

5

0

High

1

2

0

SYNC_CLK cycle

ns

ns

250

MHz

ns

ns

ms

SYSCLK cycles

μs

SYSCLK cycles

3

SYSCLK cycles

2

1

1

8

5

91

Matched latency enabled and OSK

enabled

Matched latency enabled and OSK

disabled

Matched latency disabled

Matched latency disabled

Matched latency enabled/disabled

Matched latency enabled

Matched latency disabled

Matched latency enabled/disabled

Matched latency enabled

Matched latency disabled

Matched latency enabled

Matched latency disabled

150

Frequency, Phase-to-DAC Output

79

SYSCLK cycles

Amplitude-to-DAC Output

Data Latency using RAM Mode

Frequency, Phase-to-DAC Output

Amplitude-to-DAC Output

Data Latency, Sweep Mode

Frequency, Phase-to-DAC Output

Amplitude-to-DAC Output

Data Latency, 16-Bit Input Modulation Mode

Frequency, Phase-to-DAC Output

79

47

94

106

58

91

91

47

103

91

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

SYSCLK cycles

相關PDF資料 |

PDF描述 |

|---|---|

| AD9910_07 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ-REEL | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9912 | 1 GSPS Direct Digital Synthesizer w/ 14-bit DAC |

| AD9913 | Low Power 250 MSPS 10-Bit DAC 1.8 V CMOS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9910/PCBZ | 功能描述:數據轉換 IC 開發工具 1GSPS 14 bit DDS w/ parallel input port RoHS:否 制造商:Texas Instruments 產品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| AD9910_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ | 功能描述:IC DDS 1GSPS 14BIT PAR 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9910BSVZ | 制造商:Analog Devices 功能描述:IC DDS 1GHZ TQFP-100 制造商:Analog Devices 功能描述:IC, DDS, 1GHZ, TQFP-100 |

| AD9910BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT PAR 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。