- 您現在的位置:買賣IC網 > PDF目錄360998 > ISP1161BD (NXP SEMICONDUCTORS) Full-speed Universal Serial Bus single-chip host and device controller PDF資料下載

參數資料

| 型號: | ISP1161BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | Full-speed Universal Serial Bus single-chip host and device controller |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁數: | 30/127頁 |

| 文件大小: | 2762K |

| 代理商: | ISP1161BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁

Philips Semiconductors

ISP1161

Full-speed USB single-chip host and device controller

Product data

Rev. 01 — 3 July 2001

30 of 130

9397 750 08313

Philips Electronics N.V. 2001. All rights reserved.

9.4.3

Operation & C Program Example

Figure 29

shows the block diagram for internal FIFO buffer RAM operations by PIO

mode. ISP1161 provides one register as the access port for each buffer RAM. For the

ITL buffer RAM, the access port is the ITLBufferPort register (40H - Read, C0H -

Write). For the ATL buffer RAM, the access port is the ATLBufferPort register (41H -

Read, C1H - Write). The buffer RAM is an array of bytes (8 bits) while the access port

is a 16-bit register. Therefore, each read/write operation on the port accesses two

consecutive memory locations, incrementing the pointer of the internal buffer RAM by

two.

The lower byte of the access port register corresponds to the data byte at the even

location of the buffer RAM, and the higher byte in the access port register

corresponds to the other data byte at the odd location of the buffer RAM. Regardless

of the number of data bytes to be transferred, the command code must be issued

merely once, and it will be followed by a number of accesses of the data port (see

Section 8.4

).

When the pointer of the buffer RAM reaches the value of the HcTransferCounter

register, an internal EOT signal will be generated to set bit 2, AllEOTInterrupt, of the

Hc

μ

Pinterrupt register and update the HcBufferStatus register, to indicate that the

whole data transfer has been completed.

For ITL buffer RAM, every start of frame (SOF) signal (1 ms) will cause toggling

between ITL0 and ITL1 but this depends on the buffer status. If both ITL0BufferFull

and ITL1BufferFull of the HcBufferStatus register are already logic 1, meaning that

both ITL0 and ITL1 buffer RAMs are full, the toggling will not happen. In this case, the

microprocessor will always have access to ITL1.

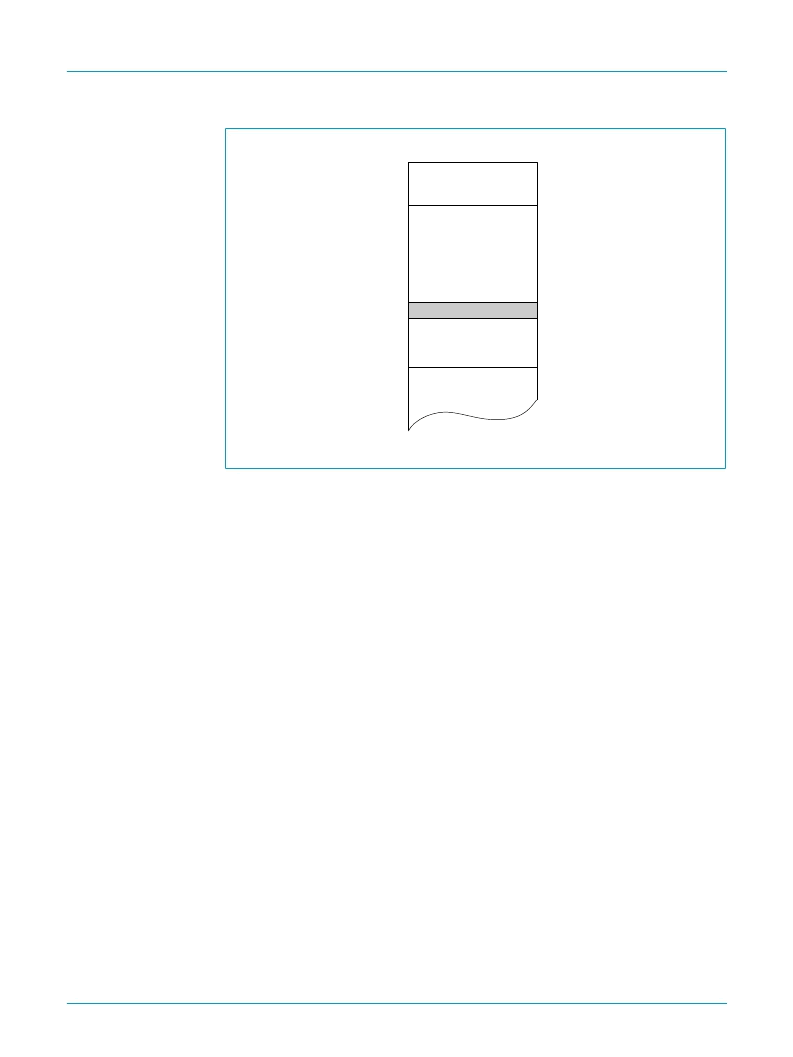

Fig 28. PTD data with DWORD alignment in buffer RAM.

MGT953

payload data

(14 bytes)

PTD

(8 bytes)

PTD

(8 bytes)

00H

top

08H

15H

18H

20H

payload data

RAM buffer

相關PDF資料 |

PDF描述 |

|---|---|

| ISP1161BM | Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1181ABS | INDUCTOR 1.0NH +-.3NH FIXED SMD |

| ISP1181A | Full-speed Universal Serial Bus peripheral controller |

| ISP1181ADGG | Full-speed Universal Serial Bus peripheral controller |

| ISP1181B | Full-speed Universal Serial Bus peripheral controller |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ISP1161BM | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1181 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus interface device |

| ISP1181A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS,518 | 功能描述:USB 接口集成電路 USB 1.1 ADV DEVICE RoHS:否 制造商:Cypress Semiconductor 產品:USB 2.0 數據速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發布緊急采購,3分鐘左右您將得到回復。