- 您現在的位置:買賣IC網 > PDF目錄382345 > MPC750 (Motorola, Inc.) Hall Effect Switch IC; Package/Case:3-SOT-23; Supply Voltage Max:24V; Current Rating:4mA; Leaded Process Compatible:Yes; Operate Point Max:90G; Operate Point Min:-90G; Operational Type:Latch; Peak Reflow Compatible (260 C):Yes RoHS Compliant: Yes PDF資料下載

參數資料

| 型號: | MPC750 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Hall Effect Switch IC; Package/Case:3-SOT-23; Supply Voltage Max:24V; Current Rating:4mA; Leaded Process Compatible:Yes; Operate Point Max:90G; Operate Point Min:-90G; Operational Type:Latch; Peak Reflow Compatible (260 C):Yes RoHS Compliant: Yes |

| 中文描述: | MPC750 RISC微處理器 |

| 文件頁數: | 26/31頁 |

| 文件大小: | 318K |

| 代理商: | MPC750 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁

26

MPC750 RISC Microprocessor Technical Summary

For More Information On This Product,

Go to: www.freescale.com

2.5 Memory Management

The following subsections describe the memory management features of the PowerPC architecture, and the

MPC750 implementation, respectively.

2.5.1 PowerPC Memory Management Model

The primary functions of the MMU are to translate logical (effective) addresses to physical addresses for

memory accesses and to provide access protection on blocks and pages of memory. There are two types of

accesses generated by the MPC750 that require address translation—instruction accesses, and data accesses

to memory generated by load, store, and cache control instructions.

The PowerPC architecture defines different resources for 32- and 64-bit processors; the MPC750

implements the 32-bit memory management model. The memory-management model provides 4 Gbytes of

logical address space accessible to supervisor and user programs with a 4-Kbyte page size and 256-Mbyte

segment size. BAT block sizes range from 128 Kbyte to 256 Mbyte and are software selectable. In addition,

it defines an interim 52-bit virtual address and hashed page tables for generating 32-bit physical addresses.

The architecture also provides independent four-entry BAT arrays for instructions and data that maintain

address translations for blocks of memory. These entries define blocks that can vary from 128 Kbytes to 256

Mbytes. The BAT arrays are maintained by system software.

The PowerPC MMU and exception model support demand-paged virtual memory. Virtual memory

management permits execution of programs larger than the size of physical memory; demand-paged implies

that individual pages are loaded into physical memory from system memory only when they are first

accessed by an executing program.

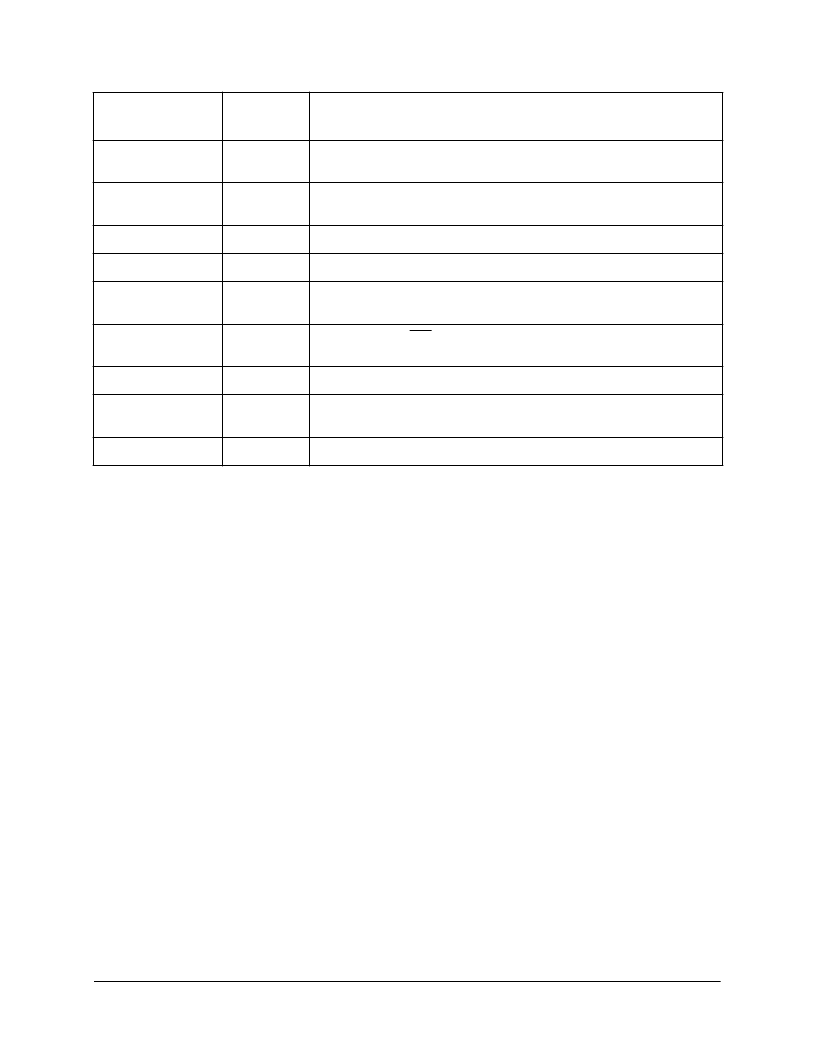

1

MPC750-specific

Trace

00D00

MSR[SE] = 1 or a branch instruction completes and MSR[BE] = 1. Unlike the

architecture definition,

isync

does not cause a trace exception.

Reserved

00E00

The MPC750 does not generate an exception to this vector. Other PowerPC

processors may use this vector for floating-point assist exceptions.

Reserved

00E10–00EFF —

Performance monitor

1

00F00

The limit specified in a PMC register is reached and MMCR0[ENINT] = 1.

Instruction address

breakpoint

1

01300

IABR[0–29] matches EA[0–29] of the next instruction to complete, IABR[TE]

matches MSR[IR], and IABR[BE] = 1.

System management

interrupt

1

01400

MSR[EE] = 1 and SMI is asserted.

Reserved

01500–016FF

—

Thermal management

interrupt

1

01700

Thermal management is enabled, the junction temperature exceeds the

threshold specified in THRM1 or THRM2, and MSR[EE] = 1.

Reserved

01800–02FFF

—

Table 5. Exceptions and Conditions (Continued)

Exception Type

Vector Offset

(hex)

Causing Conditions

F

Freescale Semiconductor, Inc.

n

.

相關PDF資料 |

PDF描述 |

|---|---|

| MPC823 | Communication Processor Module |

| MPC823UM_REV1_16-CPM7 | 10 AMP SUBMINIATURE POWER RELAY |

| MPC9109 | LOW VOLTAGE 1:18 CLOCK DISTRIBUTION CHIP |

| MPC9229 | 400 MHz Low Voltage PECL Clock Synthesizer |

| MPC9230 | 800 MHz Low Voltage PECL Clock Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MPC75-103J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Metal Plate Cement Resistors |

| MPC75-103K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Metal Plate Cement Resistors |

| MPC75201J | 功能描述:厚膜電阻器 - 透孔 MPC7 200R 5% RoHS:否 制造商:Caddock 電阻:27 kOhms 容差:1 % 功率額定值:8 W 溫度系數:50 PPM / C 系列:MS 端接類型:Axial 電壓額定值:2 kV 工作溫度范圍:- 15 C to + 275 C 尺寸:8.89 mm Dia. x 23.11 mm L 封裝:Bulk |

| MPC755 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:RISC Microprocessor Hardware Specifications |

| MPC755BPX300LE | 功能描述:微處理器 - MPU 360PBGA RV2.8 HIP4DP RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數據總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數據 RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發布緊急采購,3分鐘左右您將得到回復。