- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9898KCPRL-20 (ANALOG DEVICES INC) TVPS00RF-21-41S W/ PC CON PDF資料下載

參數資料

| 型號: | AD9898KCPRL-20 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | TVPS00RF-21-41S W/ PC CON |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | MO-220-VKKD-2, LFCSP-48 |

| 文件頁數: | 40/52頁 |

| 文件大小: | 557K |

| 代理商: | AD9898KCPRL-20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

REV. 0

–40–

AD9898

VSG TIMING

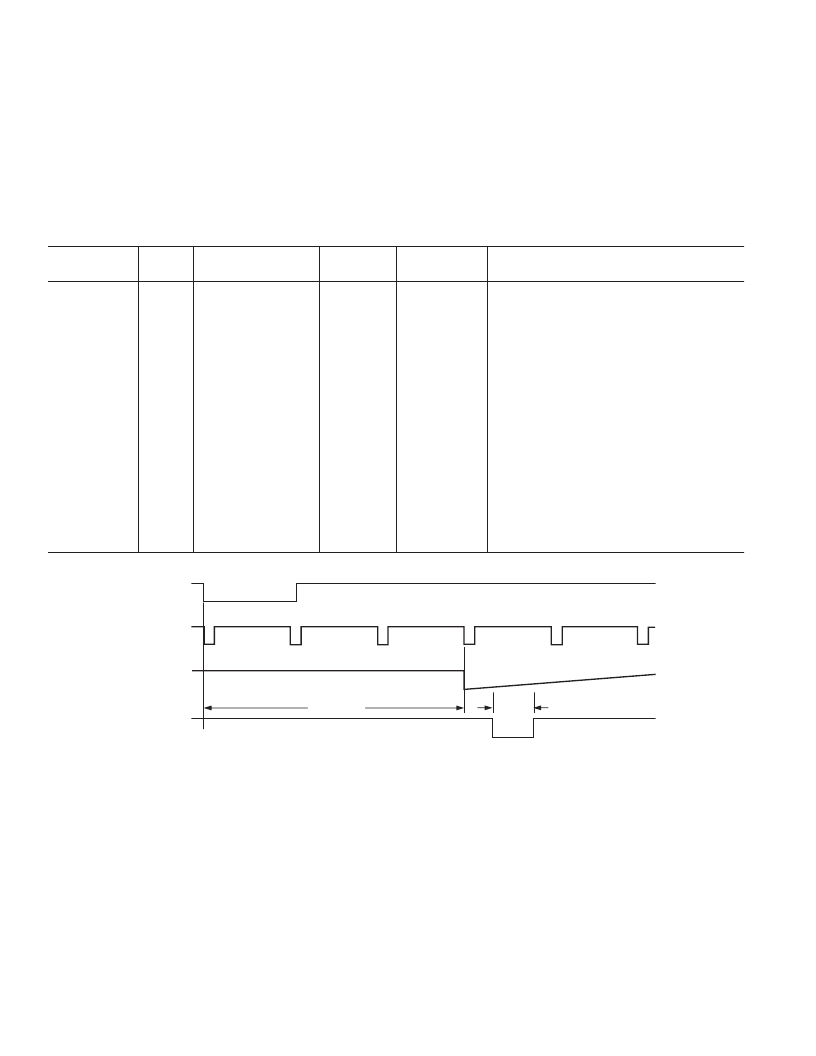

The VSG timing is controlled using the registers in Table XXIII.

Two unique preprogrammed VSG pulses can be configured

using the VSGTOG1_x (x = 0, 1) registers. As shown in

Figure 42, the period of the VSG pulse is set by programming

the VSGLEN register. The VSGSELx (x = 0, 1) can then be

used to point to either the VSGTOG1_0 or VSGTOG1_1 pulse.

1

2

3

0

VD

HD

13-BIT

ST COUNTER

(FIXED)

VSGx

1. VSGTOG1_x (x = 0, 1) REFERENCES THE 13-BIT ST COUNTER.

2. VSGACTLINE (PROGRAMMABLE AT MODE_REG (1)).

3. VSGLEN (PROGRAMMABLE AT SYS_REG (14)).

PROGRAMMABLE CLOCK POSITION

VSGTOG1_x (PROGRAMMABLE AT SYS_REG (13)).

VSGLEN

VSGACTLINE

1

Figure 42. Example of VSG Pulse

Table XXIII. VSG Registers

Register

Name

Bit

Width

Reference

Counter

Register Type

Range

Description

VSGMASK

6

Control (Addr 0x0A)

VSG Mask Control

(00 = VSG1 masked, VSG2 masked)

(02 = VSG1 not masked, VSG2 masked)

(08 = VSG1 masked, VSG2 not masked)

(0A = VSG1 not masked, VSG2 not masked)

VSG Output Enable Control

(0 = Disable VSG Outputs,

1 = Enable VSG Outputs)

VSG Sequence 1, Toggle Position 1

VSG Sequence 2, Toggle Position 1

VSG Pulsewidth

VSG1 Output Selector

(0 = VSGTOG1_0 applied on VSG1 output,

1 = VSGTOG1_1 applied on VSG1 output)

VSG2 Output Selector

(0 = VSGTOG1_0 applied on VSG2 output,

1 = VSGTOG1_1 applied on VSG2 output)

VSG Active Line

VSG_EN

1

Control (Addr 0x0B)

High/Low

VSGTOG1_0

VSGTOG1_1

VSGLEN

VSGSEL0

11

11

8

1

Sys_Reg(13)

Sys_Reg(13)

Sys_Reg(14)

Mode_Reg(1)

ST

ST

ST

0–8191 Pixels

0–8191 Pixels

0–255 Pixels

High/Low

VSGSEL1

1

Mode_Reg(1)

High/Low

VSGACTLINE

7

Mode_Reg(1)

0–128 Lines

Figure 42 also shows an example of the VSG pulse being output

in the fourth line by setting the VSGACTLINE = 3. The VSG1

and VSG2 pulses reference the 13-bit fixed ST counter, which

starts counting from the line set in the VSGACTLINE register.

The 13-bit counter allows for overlapping of the VSG pulse into

the next line, if needed.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9901 | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KQ | TVS Diode; Diode Type:Bidirectional TVS; Stand-Off Voltage, VRWM:30V; Breakdown Voltage, Vbr:33.3V; Package/Case:DO-214AB; Leaded Process Compatible:Yes; No. of Lines Protected Max:1; Peak Pulse Power PPK @ 10x1000uS:1500W RoHS Compliant: Yes |

| AD9910 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910_07 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9899ARS-2 | 制造商:Analog Devices 功能描述: |

| AD9901 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:IC VHF PHCOMP AD9901 IC - Bulk 制造商:Analog Devices 功能描述:IC DISCRIMINATOR |

| AD9901KP-REEL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:PHASE FREQ COMPARATOR IC - Tape and Reel |

| AD9901KPZ | 功能描述:IC PHS/FREQ DISCRIMINATOR 20PLCC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應商設備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

發布緊急采購,3分鐘左右您將得到回復。