- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373970 > AD9898KCPRL-20 (ANALOG DEVICES INC) TVPS00RF-21-41S W/ PC CON PDF資料下載

參數(shù)資料

| 型號(hào): | AD9898KCPRL-20 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | TVPS00RF-21-41S W/ PC CON |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | MO-220-VKKD-2, LFCSP-48 |

| 文件頁數(shù): | 44/52頁 |

| 文件大小: | 557K |

| 代理商: | AD9898KCPRL-20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

REV. 0

–44–

AD9898

STROBE Control

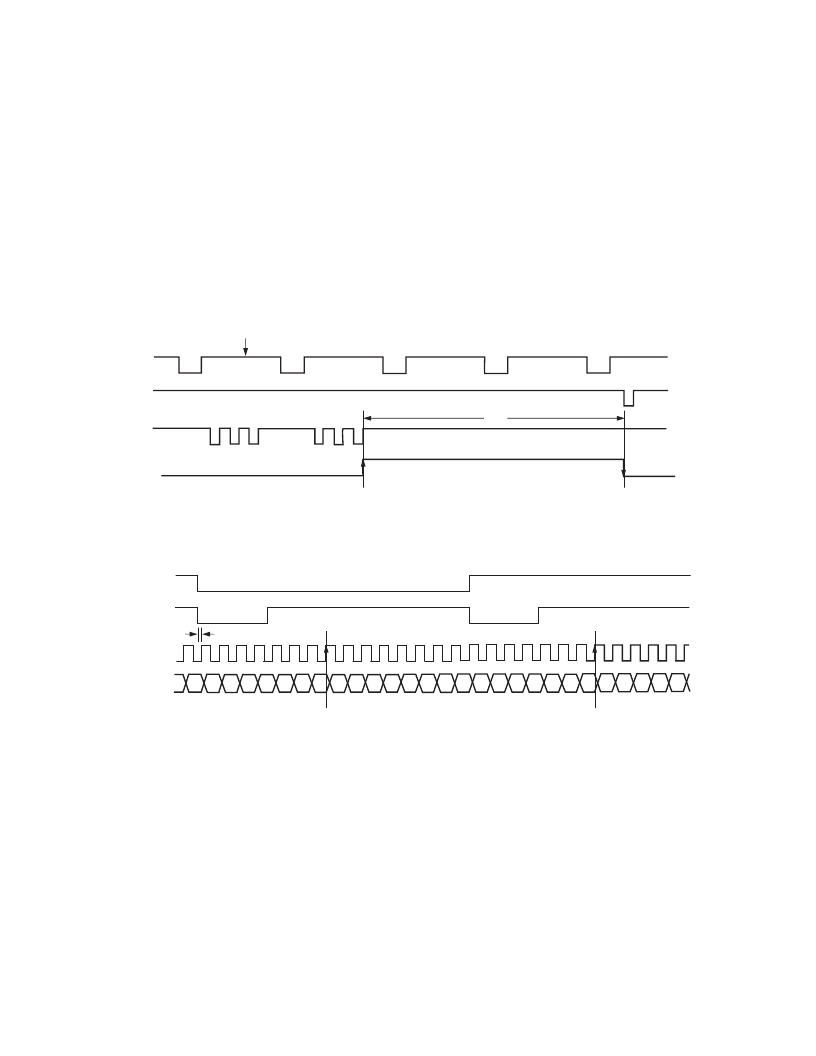

The AD9898 provides a STROBE output pulse that can be used

to trigger the camera flash circuit. STROBE operation is set by

only one register, as described in Table XXV. The STROBE

output is held Low when STROBE_EN (Addr 0x0B) is set to

0 and enabled when set to 1. Providing STROBE_EN = 1, the

STROBE output pulse will be asserted High on the rising edge of

the last SUBCK pulse in the field, as shown in Figure 48.

Figure 48 also shows the STROBE pulse asserted Low again on

the rising edge of VSG.

SLAVE AND MASTER MODE OPERATION

The AD9898 can be operated in either slave mode or master

mode. It defaults to the slave mode operation at power-up. The

1

2

1. STROBE OUTPUT ASSERTED HIGH ON RISING EDGE OF LAST SUBCK PULSE.

2. STROBE OUTPUT ASSERTED LOW ON NEGATIVE EDGE OF VSG PULSE.

SUBCK

STROBE

VSG1–

VSG2

VD

t

EXP

SET STROBE_EN (ADDR 0x0B) = 1

Figure 48. STROBE Output Timing

INTERNAL 12-BIT H-GRAY CODE COUNTER IS RESET 7 CLOCK CYCLES AFTER THE HD FALLING EDGE.

VD

HD

CLI

H-GRAY CODE

COUNTER

(PIXEL COUNTER)

X

X

X

X

X

X

X

X

X

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

0

1

2

3

4

H-COUNTER

RESET

H-COUNTER

RESET

3ns MIN

Figure 49. External VD/HD and Internal 12-Bit H-Gray Code Counter Synchronization, SLAVE Mode

SLAVE_MODE register (Addr 0xD6) can be used to configure

the AD9898 into master mode by setting SLAVE_MODE = 0.

Slave Mode Operation

While operating in slave mode, VD, HD, and VGATE are pro-

vided externally from the image processor. VGATE is input

active high on Pin 45. Unlike master mode operation, there is a

7 CLI clock cycle delay from the falling edge of HD to when the

12-bit gray code H counter is reset to zero (see Figure 49).

Master Mode Operation

While operating in master mode, VD and HD are outputs and

the SYNC/VGATE pin is configured as an external SYNC input.

Master mode is selected by setting register SLAVE_MODE

(Addr 0xD6) = 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9901 | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KQ | TVS Diode; Diode Type:Bidirectional TVS; Stand-Off Voltage, VRWM:30V; Breakdown Voltage, Vbr:33.3V; Package/Case:DO-214AB; Leaded Process Compatible:Yes; No. of Lines Protected Max:1; Peak Pulse Power PPK @ 10x1000uS:1500W RoHS Compliant: Yes |

| AD9910 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910_07 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9899ARS-2 | 制造商:Analog Devices 功能描述: |

| AD9901 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:IC VHF PHCOMP AD9901 IC - Bulk 制造商:Analog Devices 功能描述:IC DISCRIMINATOR |

| AD9901KP-REEL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:PHASE FREQ COMPARATOR IC - Tape and Reel |

| AD9901KPZ | 功能描述:IC PHS/FREQ DISCRIMINATOR 20PLCC RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時(shí)鐘 電路數(shù):1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應(yīng)商設(shè)備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。