- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9898KCPRL-20 (ANALOG DEVICES INC) TVPS00RF-21-41S W/ PC CON PDF資料下載

參數資料

| 型號: | AD9898KCPRL-20 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | TVPS00RF-21-41S W/ PC CON |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | MO-220-VKKD-2, LFCSP-48 |

| 文件頁數: | 49/52頁 |

| 文件大小: | 557K |

| 代理商: | AD9898KCPRL-20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當前第49頁第50頁第51頁第52頁

REV. 0

AD9898

–49–

HORIZONTAL TIMING SEQUENCE EXAMPLE

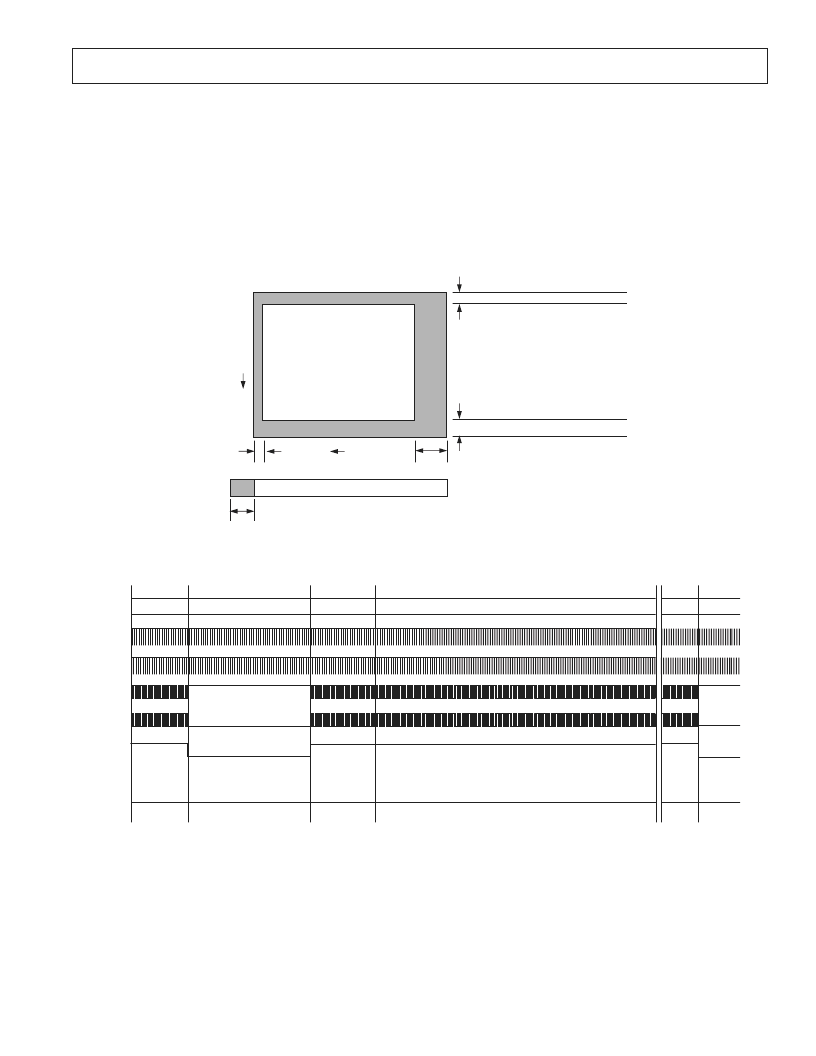

Figure 54 shows a sample CCD layout. The horizontal register

contains 28 dummy pixels, which will occur on each line clocked

from the CCD. In the vertical direction, there are 10 optical

black (OB) lines at the front of the readout and two at the back.

The horizontal direction has four OB pixels in the front and 48

in the back.

To configure the AD9898 horizontal signals for this CCD, three

sequences can be used. Figure 55 shows the first sequence to be

used during vertical blanking. During this time, there are no

EFFECTIVE IMAGE AREA

USE SEQUENCE 2

SEQUENCE 2 (OPTIONAL)

HORIZONTAL CCD REGISTER

4 OB PIXELS

48 OB PIXELS

28 DUMMY PIXELS

USE SEQUENCE 3

2 VERTICAL OB LINES

10 VERTICAL OB LINES

H

V

Figure 54. Sample CCD Configuration

SEQUENCE 1: VERTICAL BLANKING

INVALID PIX

VERTICAL SHIFT

DUMMY

INVALID PIXELS

VERT SHIFT

CDIN

SHP

SHD

H1

H2

HD

CLPOB

CLPOB PULSE MAY BE USED DURING HORIZONTAL DUMMY PIXELS

IF THE H-CLOCKS ARE USED DURING VERTICAL BLANKING.

Figure 55. Horizontal Sequence during Vertical Blanking

valid OB pixels from the sensor, so the CLPOB is not used. In

some cases, if the horizontal clocks are used during this time,

the CLPOB signal may be used to keep the AD9898’s clamp

partially settled.

Figure 56 shows the recommended sequence for the vertical OB

interval. The clamp signal is used across the whole line in order

to stabilize the clamp loop of the AD9898. Figure 57 shows the

recommended sequence for the effective pixel readout. The 48 OB

pixels at the end of each line are used for the CLPOB signal.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9901 | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KQ | TVS Diode; Diode Type:Bidirectional TVS; Stand-Off Voltage, VRWM:30V; Breakdown Voltage, Vbr:33.3V; Package/Case:DO-214AB; Leaded Process Compatible:Yes; No. of Lines Protected Max:1; Peak Pulse Power PPK @ 10x1000uS:1500W RoHS Compliant: Yes |

| AD9910 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910_07 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9899ARS-2 | 制造商:Analog Devices 功能描述: |

| AD9901 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:IC VHF PHCOMP AD9901 IC - Bulk 制造商:Analog Devices 功能描述:IC DISCRIMINATOR |

| AD9901KP-REEL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:PHASE FREQ COMPARATOR IC - Tape and Reel |

| AD9901KPZ | 功能描述:IC PHS/FREQ DISCRIMINATOR 20PLCC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應商設備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

發布緊急采購,3分鐘左右您將得到回復。