- 您現在的位置:買賣IC網 > PDF目錄367493 > L84225 L84225 100BaseTX/FX/10BaseT Physical Layer Device technical manual 4/02 PDF資料下載

參數資料

| 型號: | L84225 |

| 英文描述: | L84225 100BaseTX/FX/10BaseT Physical Layer Device technical manual 4/02 |

| 中文描述: | L84225 100BaseTX/FX/10BaseT物理層設備的技術手冊,4月2日 |

| 文件頁數: | 7/118頁 |

| 文件大小: | 890K |

| 代理商: | L84225 |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Pin Description

Copyright 1999-2002 by LSI Logic Corporation. All rights reserved.

7 of 118

April, 2002

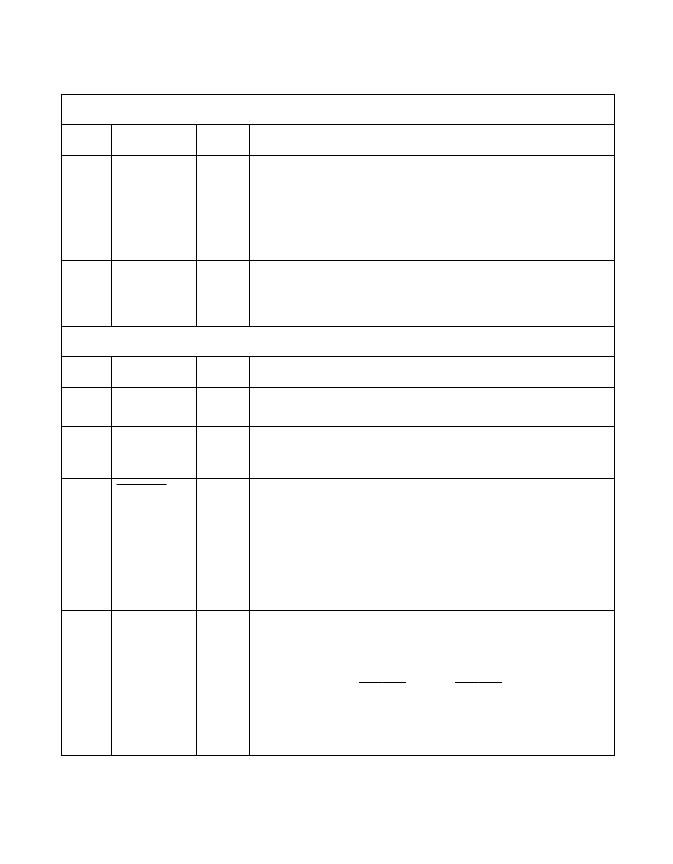

Controller Interface (MII & RMII) [Continued]

Pin #

Pin Name

I/O

Description

85

67

48

29

RXER_[3:0]/

RXD4_[3:0]

O

Receive Error Output.

These interface outputs are asserted

active high when coding or other specified errors are detected on

the TP or FX inputs and are clocked out on falling edges of

RXCLK.

If the channel is placed in the Bypass 4B5B Decoder mode, these

pins are reconfigured to be the fifth RXD receive data output,

RXD4.

93

75

57

37

COL_[3:0]

O

Collision Output.

These interface outputs are asserted active

high when collision between transmit and receive data is detected.

Management Interface (MI)

Pin #

Pin Name

I/O

Description

99

MDC

I

Management Interface (MI) Clock Input.

This MI clock shifts

serial data into and out of MDIO on rising edges.

97

MDIO

I/O

Management Interface (MI) Data Input/Output.

This bidirectional

pin contains serial data that is clocked in and out on rising edges

of the MDC clock.

98

REGDEF

I

Pullup

Invalid Register Read Select

This active low input controls the

default values that are read from invalid (unused) register

locations.

1 = All unused register locations return a value of ‘0000’ when

read.

0 = All unused register locations return a value of ‘ffff’ when read.

Note

: Not available on Rev. B product. On Rev. B product all

invalid register locations return a value of ‘0000’ when read.

20

19

18

PHYAD[4:2]

I

MI Physical Device Address Input.

These pins set the three

most significant bits of the PHY address. The two least significant

bits of the PHY address are set internally to match the channel

number, as shown below:

PHYAD1

1

1

0

0

PHYAD0

1

0

1

0

Channel 3

Channel 2

Channel 1

Channel 0

Pin Description (Cont.)

相關PDF資料 |

PDF描述 |

|---|---|

| L84302 | L84302 Quad 100/10 Mbps 4-Port Ethernet Controller with RMON/SNMP Management Counters technical manual 4/02 |

| L8560 | Low-Power SLIC with Ringing |

| L8567 | SLIC for Peoples Republic of China Applications |

| L8567-32PLCC | Telecommunication IC |

| L8567-44PLCC | Telecommunication IC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| L84225/B1 | 制造商:LSI Corporation 功能描述: |

| L8446-04 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-06 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-07 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-41 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

發布緊急采購,3分鐘左右您將得到回復。