- 您現在的位置:買賣IC網 > PDF目錄367493 > L84225 L84225 100BaseTX/FX/10BaseT Physical Layer Device technical manual 4/02 PDF資料下載

參數資料

| 型號: | L84225 |

| 英文描述: | L84225 100BaseTX/FX/10BaseT Physical Layer Device technical manual 4/02 |

| 中文描述: | L84225 100BaseTX/FX/10BaseT物理層設備的技術手冊,4月2日 |

| 文件頁數: | 9/118頁 |

| 文件大小: | 890K |

| 代理商: | L84225 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Pin Description

Copyright 1999-2002 by LSI Logic Corporation. All rights reserved.

9 of 118

April, 2002

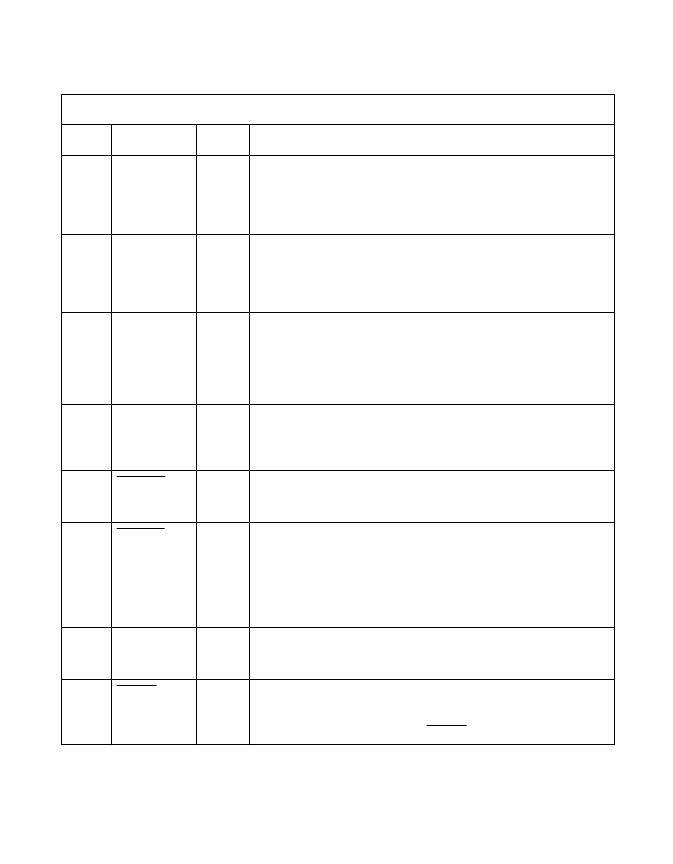

Miscellaneous

Pin #

Pin Name

I/O

Description

111

ANEG

I

AutoNegotiation Enable Input.

This digital input, ANDed with

register bit 0.12, enables AutoNegotiation for all channels.

1 = AutoNegotiation On & Combined with Speed and Duplex pins,

control advertisement. See

Table 1

for the different combinations.

0 = Off

120

119

113

112

SPEED_[3:0]

I

Speed Selection Input.

These digital inputs, ANDed with register

bit 0.13, select speed in each corresponding channel. Please refer

to

Table 1

for the different combinations.

1 = 100 Mbps Mode

0 = 10 Mbps Mode

103

104

105

106

DPLX_[3:0]

I

Duplex Selection Input.

These digital inputs, ORed with register

bit 0.8, select the duplex mode in EACH corresponding channel.

They control advertisement when ANEG is enabled. See

Table 1

for the different combinations.

1 = Full Duplex Mode

0 = Half Duplex Mode

102

REPEATER

I

Repeater Mode Enable Input.

This digital input, ORed with reg-

ister bit 17.14, enables repeater mode for ALL channels.

1 = Repeater Mode Enabled

0 = Normal Operation

101

RMII_EN

I

Reduced Pin Count MII Interface Enable.

1 = RMII Mode Enabled

0 = MII Enabled

17

AD_REV

I

Pullup

Address Reverse Input.

1 = Normal

In this mode, physical ports 0-3 are mapped to MI addresses 0-3

in the same order.

0 = Reverse Address Mode Select

In this mode, physical ports 0-3 are mapped to MI addresses 3-0

respectively. This is the reverse to the normal order.

118

CLKIN

I

Clock Input.

In MII mode, there must be a 25 MHz clock input to

this pin. In RMII mode, there must be a 50 MHz clock input to this

pin. TXCLK is generated from the input to this pin.

109

RESET

I

Pullup

Hardware Reset Input.

1 = Normal

0 = Device In Reset State

(Reset is complete 50 ms after RESET goes high).

Pin Description (Cont.)

相關PDF資料 |

PDF描述 |

|---|---|

| L84302 | L84302 Quad 100/10 Mbps 4-Port Ethernet Controller with RMON/SNMP Management Counters technical manual 4/02 |

| L8560 | Low-Power SLIC with Ringing |

| L8567 | SLIC for Peoples Republic of China Applications |

| L8567-32PLCC | Telecommunication IC |

| L8567-44PLCC | Telecommunication IC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| L84225/B1 | 制造商:LSI Corporation 功能描述: |

| L8446-04 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-06 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-07 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

| L8446-41 | 制造商:HAMAMATSU 制造商全稱:Hamamatsu Corporation 功能描述:CW LASER DIODES |

發布緊急采購,3分鐘左右您將得到回復。