- 您現在的位置:買賣IC網 > PDF目錄382738 > Z550 Telecomm/Datacomm PDF資料下載

參數資料

| 型號: | Z550 |

| 元件分類: | 通信、網絡模塊及開發工具 |

| 英文描述: | Telecomm/Datacomm |

| 中文描述: | 電信/數據通信 |

| 文件頁數: | 11/30頁 |

| 文件大小: | 581K |

| 代理商: | Z550 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––

I

Z550 UART

I

11

Oki Semiconductor

Modem Status Register

The Modem Status Register (MSR) provides the CPU with status of the modem input lines from modems

or peripheral devices. The MSR allows the CPU to read the serial channel modem signal inputs by access-

ing the data bus interface of the ACE. In addition to the current status information, four bits of the MSR

indicate whether the modem inputs have changed since the last reading of the MSR. The delta status bus

are set high when a control input from the modem changes state, and reset low when the CPU reads the

MSR.

The modem input lines are CTS, DSR, RI, and DCD. MSR(4) - MSR(7) are status indications of these lines.

A status bit = 1 indicates the input is a low. A status bit = 0 indicates the input is high. If the modem status

interrupt in the Interrupt Enable Register is enabled [IER(3)=1] an interrupt is generated whenever

MCR(3):

When MCR(3) is set high, the OUT2 output is forced low. When MCR(3) is reset low, the OUT2

output is forced high.

MCR(4):

MCR(4) provides a local loop back feature for diagnostic testing. When MCR(4) is set high, Serial

Output (SOUT) is set to the marking (logic “1”) state. The receiver data input, Serial Input (SIN)

is disconnected and the output of the Transmitter Shift Register is looped back into the Receiver

Shift Register input. The four modem control inputs (CTS, DSR, DCD, and RI) are disconnected.

The four MCR bits DTR, RTS, OUT1, and OUT2 are internally connected to MSR(5), MSR(4),

MSR(6), and MSR(7) in that order. The modem control output pins are forced to their inactive

state (high).

In the diagnostic mode, data transmitted is immediately received. This allows the processor to

verify the transmit and receive data paths of the selected serial channel.

Interrupt control is fully operational. However, interrupts are generated by controlling the lower

four MCR bits internally. Interrupts are not generated by activity on the external pins represented

by those four bus.

Bits MCR(5) - MCR(7):

Permanently set to logic “0”.

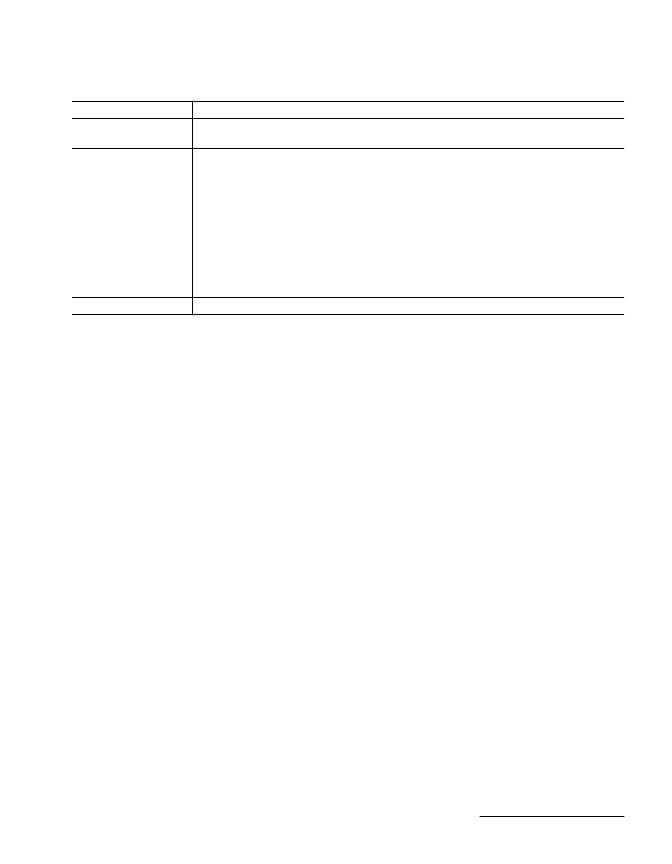

Modem Control Register Description (Continued)

MCR Bit(s)

Bit Description

相關PDF資料 |

PDF描述 |

|---|---|

| Z5904 | Leaded Cartridge Fuse; Current Rating:1A; Voltage Rating:250V; Fuse Terminals:Axial Lead; Fuse Type:Time Delay; Body Material:Glass; Diameter:4.5mm; Fuse Size/Group:5 x 15 mm; Leaded Process Compatible:No; Length:14.48mm |

| Z6000(MLBA2) | FUSE,FAST ACTING,3A,250VAC |

| Z6005 | 3A 250V SLO-BLO NR 5X20MM |

| Z6006 | TANK SPRAY WASH |

| Z6011 | PCB PROCESSOR 3 SYSTEM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| Z550LA40A | 制造商:HVCA & CKE 功能描述:RADIAL LEAD MOV - LINE VOLTAGE - STANDARD ENERGY, 1500V, 50A, 180PF |

| Z550LA80A | 制造商:HVCA & CKE 功能描述:Varistor, MO; 910V; 6500A; 350pF |

| Z550MC10 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:Z550 SENSOR HEAD 制造商:OMRON Industrial Automation 功能描述:Z550 SENSOR HEAD |

| Z550-MC10 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:Z550 SENSOR HEAD 制造商:OMRON Industrial Automation 功能描述:Z550 SENSOR HEAD 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:Z550 Sensor Head |

| Z550MC15 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:Z550 SENSOR HEAD |

發布緊急采購,3分鐘左右您將得到回復。