- 您現在的位置:買賣IC網 > PDF目錄382723 > UJA1061 (NXP Semiconductors N.V.) Low speed CAN/LIN system basis chip PDF資料下載

參數資料

| 型號: | UJA1061 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Low speed CAN/LIN system basis chip |

| 中文描述: | 低高速CAN / LIN系統(tǒng)基礎芯片 |

| 文件頁數: | 30/81頁 |

| 文件大小: | 323K |

| 代理商: | UJA1061 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

2004 Mar 22

30

Philips Semiconductors

Objective specification

Low speed CAN/LIN system basis chip

UJA1061

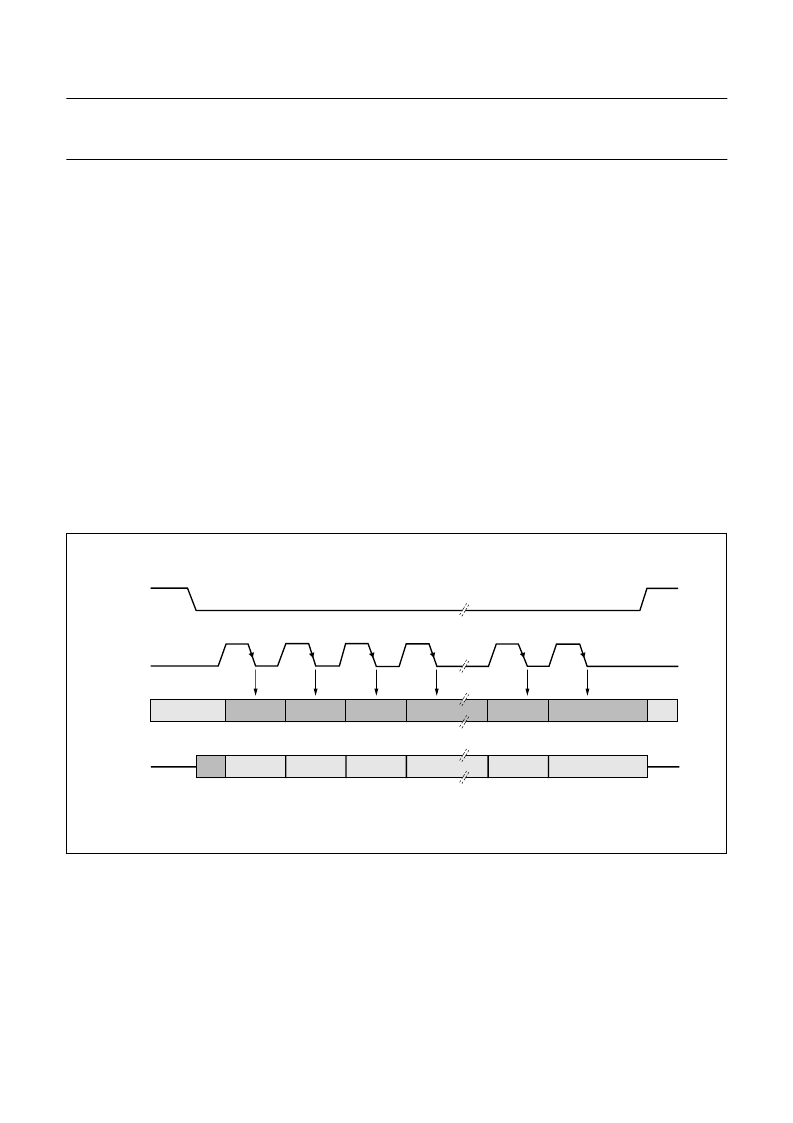

The following SPI interface signals are implemented:

SCS - SPI chip select; active LOW

SCK - SPI clock; default level is LOW due to low-power

concept

SDI - SPI data input

SDO - SPI data output; floating when pin SCS is HIGH.

The SPI interface can be accessed only when pin RSTN

(input channel of RSTN) is set HIGH.

Possible SPI failures are:

SPI clock count failure (wrong number of clock cycles

during one SPI access). Within one SCS cycle only

16 clock periods are allowed. Any deviation from the

16 clock cycles results in an SPI failure interrupt, if

enabled. The access is ignored by the UJA1061. In

Start-up and Restart mode, a reset is forced instead of

an interrupt

Wrong mode register code. The following events result

in an immediate system reset without interrupt

according to the state diagram of the system controller

– Mode other than initializing Normal mode selected

within mode register in Start-up or Restart mode

– Initializing Flash mode outside of Start-up mode or

within Start-up mode without previous Flash

sequence

– Bit WDD set in the mode register; this bit may only be

set via the special mode register

– Illegal watchdog period coding, see Section 6.14.2.

Illegal mode register code during Normal or Standby

mode of the UJA1061.

With a read-only access to the system status register or

the system diagnosis register which, with the mode

register, share the same SPI address, the data written to

the mode register is ‘don’t care’ and is ignored. Reading

these two system registers is allowed at any time

independent of watchdog window cycles.

handbook, full pagewidth

SCK

01

sampled

floating

floating

MCE634

X

X

MSB

14

13

12

01

LSB

MSB

14

13

12

01

LSB

X

SDI

SDO

02

03

04

15

16

Fig.13 SPI timing protocol.

相關PDF資料 |

PDF描述 |

|---|---|

| UJA1065 | High-speed CAN/LIN fail-safe system basis chip |

| UL631H256 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C35 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C35G1 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C45 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UJA1061_10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Fault-tolerant CAN/LIN fail-safe system basis chip |

| UJA1061TW | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Fault-tolerant CAN/LIN fail-safe system basis chip |

| UJA1061TW/3V0,512 | 制造商:NXP Semiconductors 功能描述: |

| UJA1061TW/3V0512 | 制造商:NXP Semiconductors 功能描述:CONTROLLER SYS CAN/LIN 3V 32HTSSOP |

| UJA1061TW/3V3/C/T, | 功能描述:CAN 接口集成電路 FT CAN/LIN fail-safe system basis chip RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。