- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9910BSVZ-REEL (ANALOG DEVICES INC) 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9910BSVZ-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| 中文描述: | SERIAL, PARALLEL, WORD INPUT LOADING, 14-BIT DAC, PDSO100 |

| 封裝: | ROHS COMPLIANT, MS-026AED-HD, TQFP-100 |

| 文件頁數: | 11/60頁 |

| 文件大小: | 764K |

| 代理商: | AD9910BSVZ-REEL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9910

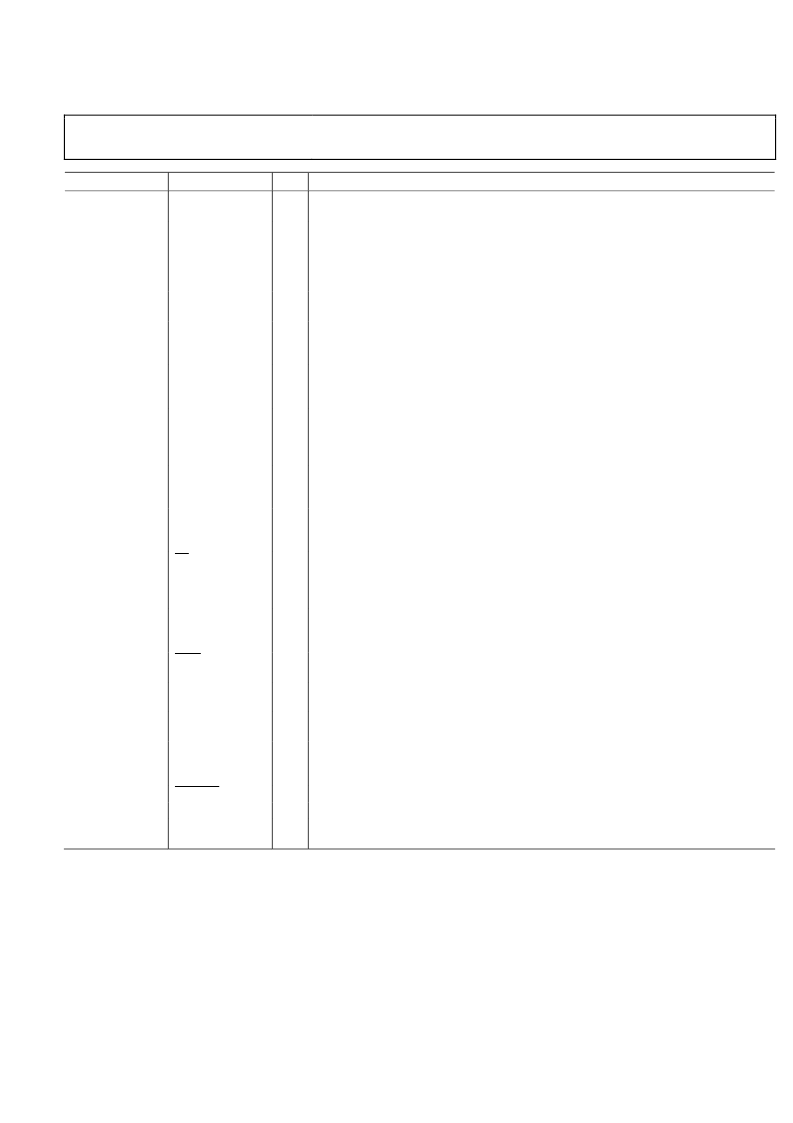

Pin No.

59

Rev. 0 | Page 11 of 60

Mnemonic

I/O_UPDATE

I/O

1

I

Description

Input/Output Update. Digital input (active high). A high on this pin transfers the contents

of the I/O buffers to the corresponding internal registers.

Output Shift Keying. Digital input (active high). When the OSK features are placed in either

manual or automatic mode, this pin controls the OSK function. In manual mode, it toggles

the multiplier between 0 (low) and the programmed amplitude scale factor (high). In

automatic mode, a low sweeps the amplitude down to zero, a high sweeps the amplitude

up to the amplitude scale factor.

Digital Ramp Over. Digital output (active high). This pin switches to Logic 1 whenever the

digital ramp generator reaches its programmed upper or lower limit.

Digital Ramp Control. Digital input (active high). This pin controls the slope polarity of the

digital ramp generator. See the Digital Ramp Generator (DRG) section for more details. If

not using the digital ramp generator, connect this pin to Logic 0.

Digital Ramp Hold. Digital input (active high). This pin stalls the digital ramp generator in

its present state. See the Digital Ramp Generator (DRG) section for more details. If not

using digital ramp generator, connect this pin to Logic 0.

Serial Data Input/Output. Digital input/output (active high). This pin can be either uni-

directional or bidirectional (default), depending on the configuration settings. In bidirectional

serial port mode, this pin acts as the serial data input and output. In unidirectional mode,

it is an input only.

Serial Data Output. Digital output (active high). This pin is only active in unidirectional

serial data mode. In this mode, it functions as the output. In bidirectional mode, this pin is

not operational and should be left floating.

Serial Data Clock. Digital clock (rising edge on write, falling edge on read). This pin

provides the serial data clock for the control data path. Write operations to the AD9910 use

the rising edge. Readback operations from the AD9910 use the falling edge.

Chip Select. Digital input (active low). This pin allows the AD9910 to operate on a common

serial bus for the control data path. Bringing this pin low enables the AD9910 to detect

serial clock rising/falling edges. Bringing this pin high causes the AD9910 to ignore input

on the serial data pins.

Input/Output Reset. Digital input (active high). This pin can be used when a serial I/O

communication cycle fails (see the I/O_RESET—Input/Output Reset section for details).

When not used, connect this pin to ground.

Open Source DAC Complementary Output Source. Analog output (current mode). Connect

through a 50 Ω resistor to AGND.

Open Source DAC Output Source. Analog output (current mode). Connect through a 50 Ω

resistor to AGND.

Analog Reference Pin. This pin programs the DAC output full-scale reference current.

Attach a 10 kΩ resistor to AGND.

Reference Clock Input. Analog input. When the internal oscillator is engaged, this pin can

be driven by either an external oscillator or connected to a crystal. See the REF_CLK

Overview section for more details.

Reference Clock Input. Analog input. See the REF_CLK Overview section for more details.

Crystal Output. Analog output. See the REF_CLK Overview section for more details.

Crystal Select. Analog input (active high). Driving the XTAL_SEL pin high, the AVDD (1.8V)

enables the internal oscillator to be used with a crystal resonator. If unused, connect it to AGND.

60

OSK

I

61

DROVER

O

62

DRCTL

I

63

DRHOLD

I

67

SDIO

I/O

68

SDO

O

69

SCLK

I

70

CS

I

71

I/O_RESET

I

80

IOUT

O

81

IOUT

O

84

DAC_RSET

O

90

REF_CLK

I

91

94

95

REF_CLK

REFCLK_OUT

XTAL_SEL

I

O

I

1

I = input, O = output.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9912 | 1 GSPS Direct Digital Synthesizer w/ 14-bit DAC |

| AD9913 | Low Power 250 MSPS 10-Bit DAC 1.8 V CMOS Direct Digital Synthesizer |

| AD9913BCPZ1 | Low Power 250 MSPS 10-Bit DAC 1.8 V CMOS Direct Digital Synthesizer |

| AD9913BCPZ-REEL71 | Low Power 250 MSPS 10-Bit DAC 1.8 V CMOS Direct Digital Synthesizer |

| AD9920A | 12-Bit CCD Signal Processor with V-Driver and Precision Timing Generator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9911 | 制造商:AD 制造商全稱:Analog Devices 功能描述:500 MSPS Direct Digital Synthesizer with 10-Bit DAC |

| AD9911/PCB | 制造商:Analog Devices 功能描述:500 MSPS DIRECT DGTL SYNTHESIZER W/ 10-BIT DAC AD9911/PCB - Bulk |

| AD9911/PCBZ | 功能描述:BOARD EVAL FOR AD9911 RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:AgileRF™ 標準包裝:1 系列:PCI Express® (PCIe) 主要目的:接口,收發器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要屬性:- 次要屬性:- 已供物品:板 |

| AD9911BCPZ | 功能描述:IC DDS 500MSPS DAC 10BIT 56LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9911BCPZ-REEL7 | 功能描述:IC DDS 500MSPS DAC 10BIT 56LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。