- 您現在的位置:買賣IC網 > PDF目錄371046 > MC68CK338 (Motorola, Inc.) Highly Integrated, Low-Power, 32-Bit Microcontroller PDF資料下載

參數資料

| 型號: | MC68CK338 |

| 廠商: | Motorola, Inc. |

| 元件分類: | 32位微控制器 |

| 英文描述: | Highly Integrated, Low-Power, 32-Bit Microcontroller |

| 中文描述: | 高度集成,低功耗,32位微控制器 |

| 文件頁數: | 71/133頁 |

| 文件大小: | 798K |

| 代理商: | MC68CK338 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當前第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁

MC68CK338

MC68CK338TS/D

MOTOROLA

71

Information to be transmitted must be written to transmit data RAM in a right-justified format. The QSPI

cannot modify information in the transmit data RAM. The QSPI copies the information to its data serial-

izer for transmission. Information remains in transmit RAM until overwritten.

Command RAM is used by the QSPI when in master mode. The CPU writes one byte of control infor-

mation to this segment for each QSPI command to be executed. The QSPI cannot modify information

in command RAM.

Command RAM consists of 16 bytes. Each byte is divided into two fields. The peripheral chip-select

field enables peripherals for transfer. The command control field provides transfer options.

A maximum of 16 commands can be in the queue. Queue execution by the QSPI proceeds from the

address in NEWQP[3:0] through the address in ENDQP[3:0]. (Both of these fields are in SPCR2).

CONT — Continue

0 = Control of chip selects returned to PORTQS after transfer is complete.

1 = Peripheral chip selects remain asserted after transfer is complete.

BITSE — Bits per Transfer Enable

0 = 8 bits

1 = Number of bits set in BITS[3:0] field of SPCR0

DT — Delay after Transfer

The QSPI provides a variable delay at the end of serial transfer to facilitate the interface with peripherals

that have a latency requirement. The delay between transfers is determined by the SPCR1 DTL[6:0]

field.

DSCK — PCS to SCK Delay

0 = PCS valid to SCK transition is one-half SCK.

1 = SPCR1 DSCKL[6:0] field specifies delay from PCS valid to SCK.

PCS[3:0] — Peripheral Chip Select

Use peripheral chip-select bits to select an external device for serial data transfer. More than one pe-

ripheral chip select can be activated at a time, and more than one peripheral chip can be connected to

each PCS pin, provided that proper fanout is observed.

NOTES:

1.

The PCS0 bit represents the dual-function PCS0/SS

.

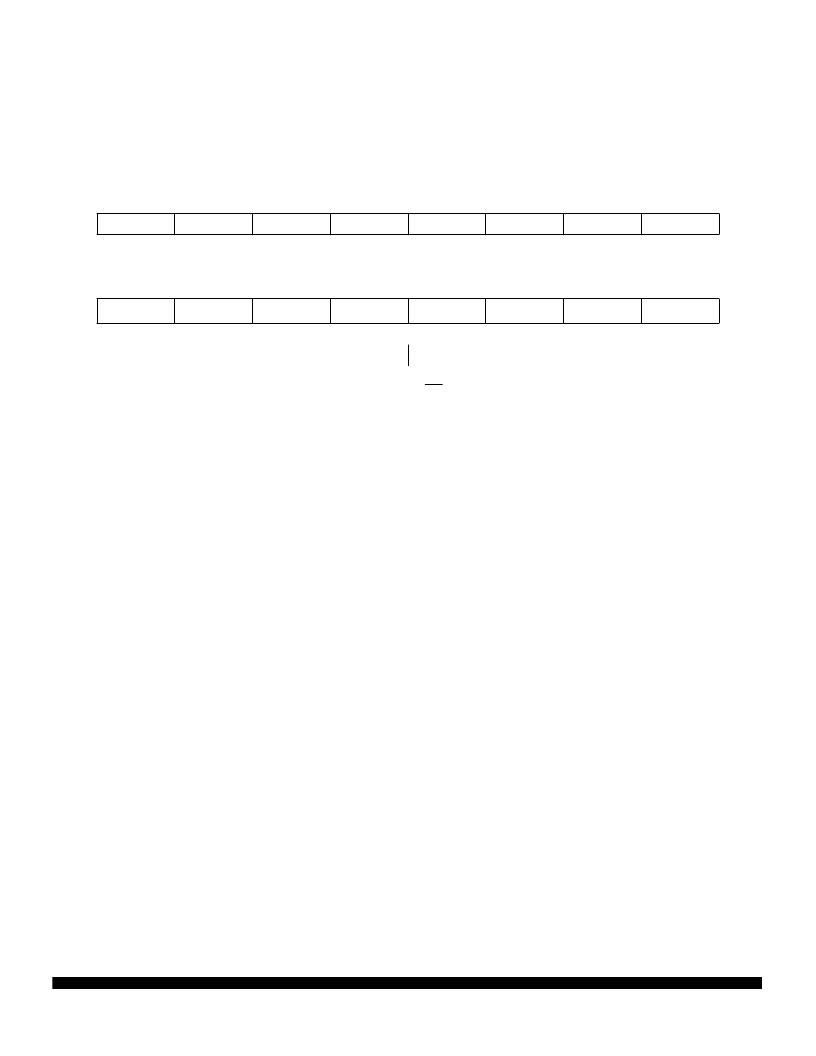

CR[0:F] —

Command RAM

$YFFD40

7

6

5

4

3

2

1

0

CONT

BITSE

DT

DSCK

PCS3

PCS2

PCS1

PCS0

1

–

–

–

–

–

–

–

–

CONT

BITSE

DT

DSCK

PCS3

PCS2

PCS1

PCS0

1

COMMAND CONTROL

PERIPHERAL CHIP SELECT

相關PDF資料 |

PDF描述 |

|---|---|

| MC68EC060 | 32-Bit Microprocessors.(32位微處理器) |

| MC68EN360RC25V | QUad Integrated Communications Controller Users Manual |

| MC68EN360CFE25 | QUad Integrated Communications Controller Users Manual |

| MC68EN360FE25 | AC 4C 4#12 PIN PLUG 023 |

| MC68EN360FE25V | QUad Integrated Communications Controller Users Manual |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC68CK338CPV14 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68CK338CPV14B1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68CM16Z1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CM16Z1CFC16 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CM16Z1CPV16 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

發布緊急采購,3分鐘左右您將得到回復。