- 您現在的位置:買賣IC網 > PDF目錄382347 > MR82510 (Intel Corp.) ASYNCHRONOUS SERIAL CONTROLLER PDF資料下載

參數資料

| 型號: | MR82510 |

| 廠商: | Intel Corp. |

| 英文描述: | ASYNCHRONOUS SERIAL CONTROLLER |

| 中文描述: | 異步串行控制器 |

| 文件頁數: | 15/40頁 |

| 文件大小: | 463K |

| 代理商: | MR82510 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

M82510

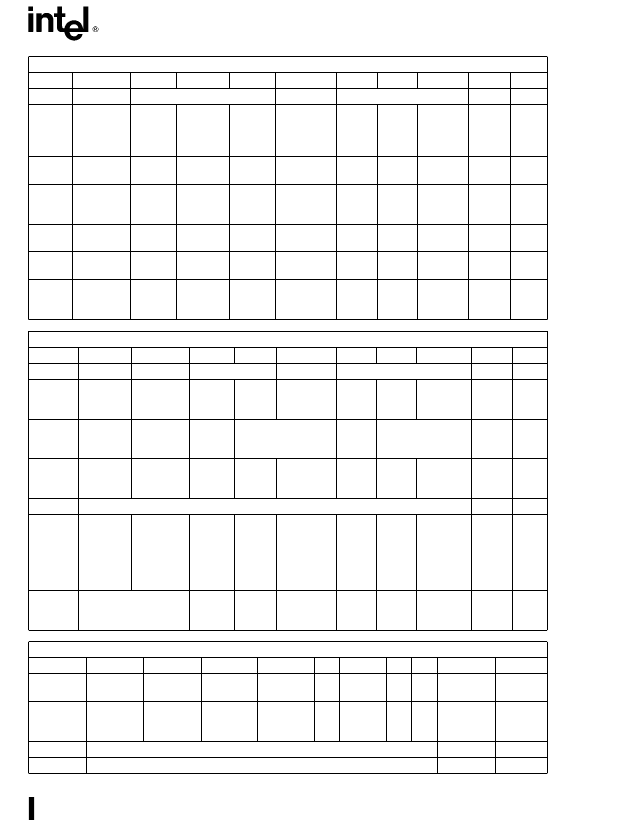

BANK ONEDGENERAL WORK BANK

(Continued)

Register

7

6

5

4

3

2

1

0

Address Default

FLR (25)

D

Rx FIFO Level

D

Tx FIFO Level

4

00H

RST (23) Address/

Address/ Break

Control

Character

Match

Break

Framing

Error

Parity

Error

Overrun Rx FIFO

Error

5

00H

Control

Character

Received

Terminated Detected

Interrupt

Requested

RCM (30) Rx

Rx

Disable

Flush

RxM

Flush

Rx FIFO

Lock Rx

FIFO

Open Rx

FIFO

0

0

5

D

Enable

MSR (27) DCD

RI Input

DSR Input

Inverted

CTS Input State

Inverted

State

Change

in RI

State

Change Change

in DSR

State

6

00H

Complement Inverted

Change

in DCD

in CTS

TCM (29)

0

0

0

0

Flush Tx

Machine

Flush Tx Tx

FIFO

Tx

Disable

6

D

Enable

GSR (20)

D

D

Timer

Interrupt

TxM

Interrupt

Modem

Interrupt

RxM

Interrupt Interrupt Interrupt

Tx FIFO Rx FIFO

7

12H

ICM (28)

0

0

0

Software

Reset

Manual Int

Acknowledge Clear

Command

Status

Power

Down

Mode

0

7

D

BANK TWODGENERAL CONFIGURATION

Register

7

6

5

4

3

2

1

0

Address Default

FMD (4)

0

0

Rx FIFO Threshold

0

0

Tx FIFO Threshold

1

00H

GIR/BANK

(21)

0

BANK

Pointer

bit 1

BANK

Pointer

bit 0

0

Active

Block Int

bit 2

Active

Block Int Block Int Pending

bit 1

bit 0

Active

Interrupt

2

01H

TMD (3)

Error

Echo

Disable

Control

Character

Echo Disable Length

9-bit

Character

Transmit Mode

Software

Parity

Mode

Stop Bit Length

3

00H

IMD (1)

0

0

0

0

Interrupt

Acknowledge Depth

Mode

Rx FIFO ulan

Loopback or

Echo Mode

of Operation

4

0CH

Mode

Select

ACR1 (6)

Address or Control Character 1

5

00H

RIE (17)

Address/

Control

Character

Recognition Match

Interrupt

Enable

Address/

Control

Character

Break

Terminate Detect

Interrupt

Enable

Break

Framing

Error

Parity

Error

Interrupt Interrupt

Enable

Overrun

Error

0

6

1EH

Interrupt Interrupt

Enable

Enable

Enable

Interrupt

Enable

RMD (7)

Address/Control

Character Mode

Disable

DPLL

Sampling Start bit

Window

Mode

0

0

0

7

00H

Sampling

Mode

BANK THREEDMODEM CONFIGURATION

Register

7

6

5

4

3

2

1

0

Address

Default

CLCF (8)

Rx Clock

Mode

Rx Clock

Source

Tx Clock

Mode

Tx Clock

Source

0

0

0

0

0

00H

BACF (9)

0

BRGA

Clock

Source

0

0

0

BRGA

Mode

0

0

1

04H

BBL (13)

BRGB LSB Divide Count (DLAB

e

1)

0

05H

BBH (14)

BRGB MSB Divide Count (DLAB

e

1)

1

00H

15

相關PDF資料 |

PDF描述 |

|---|---|

| MR8251A | PROGRAMMABLE COMMUNICATION INTERFACE |

| MR851G | Axial Lead Fast Recovery Rectifiers |

| MR851RL | Axial Lead Fast Recovery Rectifiers |

| MR851RLG | Axial Lead Fast Recovery Rectifiers |

| MR852G | Axial Lead Fast Recovery Rectifiers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MR82510/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8251A | 制造商:Intel 功能描述: |

| MR8251A/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8254/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8254/R | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。