- 您現在的位置:買賣IC網 > PDF目錄382347 > MR82510 (Intel Corp.) ASYNCHRONOUS SERIAL CONTROLLER PDF資料下載

參數資料

| 型號: | MR82510 |

| 廠商: | Intel Corp. |

| 英文描述: | ASYNCHRONOUS SERIAL CONTROLLER |

| 中文描述: | 異步串行控制器 |

| 文件頁數: | 6/40頁 |

| 文件大小: | 463K |

| 代理商: | MR82510 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

M82510

271072–4

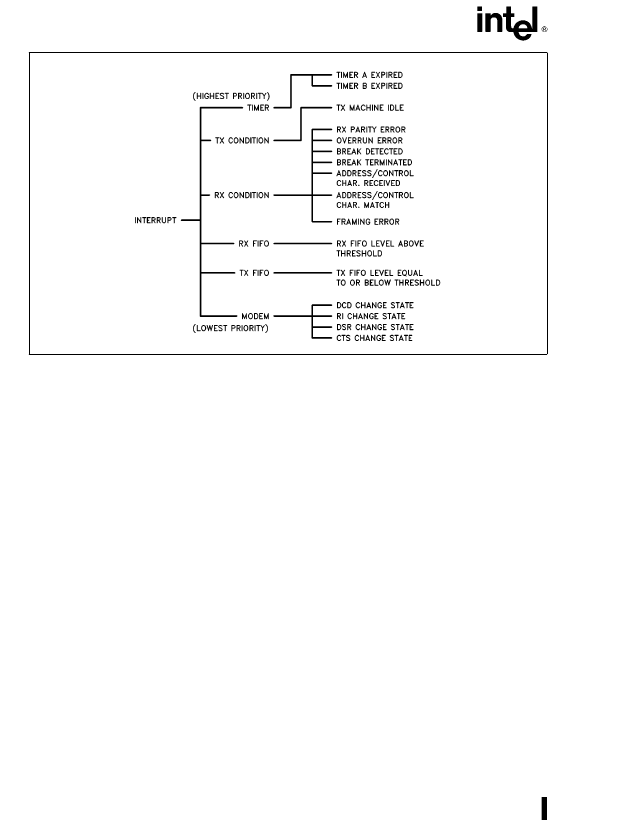

Figure 4. Interrupt Structure

Interrupts

There are two levels of interrupt/status reporting

within the M82510. The first level is the block level

interrupts such as RX FIFO, Tx FIFO, Rx Machine,

Tx Machine, Timing unit, and Modem Module. The

status of these blocks is reported in the General

Status and General Interrupt Registers. The second

level is the various sources within each block; only

three of the blocks generate second level interrupts

(Rx Machine, Timing Unit, and Modem Module). In-

terrupt requests are maskable at both the block level

and at the individual source level within the module.

If more than one unmasked block requests interrupt

service an on-chip interrupt controller will resolve

contention on a priority basis (each block has a fixed

priority). An interrupt request from a particular block

is activated if one of the unmasked status bits within

the status register for the block is set. A CPU service

operation, e.g., reading the appropriate status regis-

ter, will reset the status bits.

ACKNOWLEDGE MODES

The interrupt logic will assert the INT pin when an

interrupt is coded into the General Interrupt register.

The INT pin is forced low upon acknowledgment.

The M82510 has two modes of interrupt acknowl-

edgment:

1. Manual Acknowledge

The CPU must issue an explicit Interrupt Acknowl-

edge command via the Interrupt Acknowledge bit of

the Internal Command register. As a result the INT

pin is forced low for two clocks and then updated.

2. Automatic Acknowledge

As opposed to the Manual Acknowledge mode,

when the CPU must issue an explicit interrupt ac-

knowledge command, an interrupt service operation

is considered as an automatic acknowledgment.

This forces the INT pin low for two clock cycles.

After two cycles the INT pin is updated, i.e., if there

is still an active non-masked interrupt request the

INT pin is set HIGH.

INTERRUPT SERVICE

A service operation is an operation performed by the

CPU, which causes the source of the M82510 inter-

rupt to be reset (it will reset the particular status bit

causing the interrupt). An interrupt request within the

M82510 will not reset until the interrupt source has

been serviced. Each source can be serviced in two

or three different ways; one general way is to disable

the particular status bit causing the interrupt, via the

corresponding block enable register. Setting the ap-

propriate bit of the enable register to zero will mask

off the corresponding bit in the status register, thus

causing an edge on the input line to the interrupt

logic. The same effect can be achieved by masking

6

相關PDF資料 |

PDF描述 |

|---|---|

| MR8251A | PROGRAMMABLE COMMUNICATION INTERFACE |

| MR851G | Axial Lead Fast Recovery Rectifiers |

| MR851RL | Axial Lead Fast Recovery Rectifiers |

| MR851RLG | Axial Lead Fast Recovery Rectifiers |

| MR852G | Axial Lead Fast Recovery Rectifiers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MR82510/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8251A | 制造商:Intel 功能描述: |

| MR8251A/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8254/B | 制造商:Rochester Electronics LLC 功能描述: |

| MR8254/R | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。