- 您現在的位置:買賣IC網 > PDF目錄382369 > P90CL301BFH (NXP SEMICONDUCTORS) Low voltage 16-bit microcontroller PDF資料下載

參數資料

| 型號: | P90CL301BFH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Low voltage 16-bit microcontroller |

| 中文描述: | 16-BIT, 27.02 MHz, MICROCONTROLLER, PQFP80 |

| 文件頁數: | 17/92頁 |

| 文件大?。?/td> | 526K |

| 代理商: | P90CL301BFH |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

1996 Dec 11

17

Philips Semiconductors

Preliminary specification

Low voltage 16-bit microcontroller

P90CL301BFH (C100)

Table 18

Description of LIR0 to LIR3 bits

6.7.2.2

Pending Interrupt Flag Register (PIFR)

An additional register PIFR contains copies of the PIR flags. The PIF flags are set at the same time as the PIR flags when

an interrupt is activated, but these flags are not reset automatically during the interrupt acknowledge cycle. They can only

be cleared by software and keep a trace of the interrupt event. The detection of an external interrupt is indicated by the

corresponding PIF-bit being set to a logic 1.

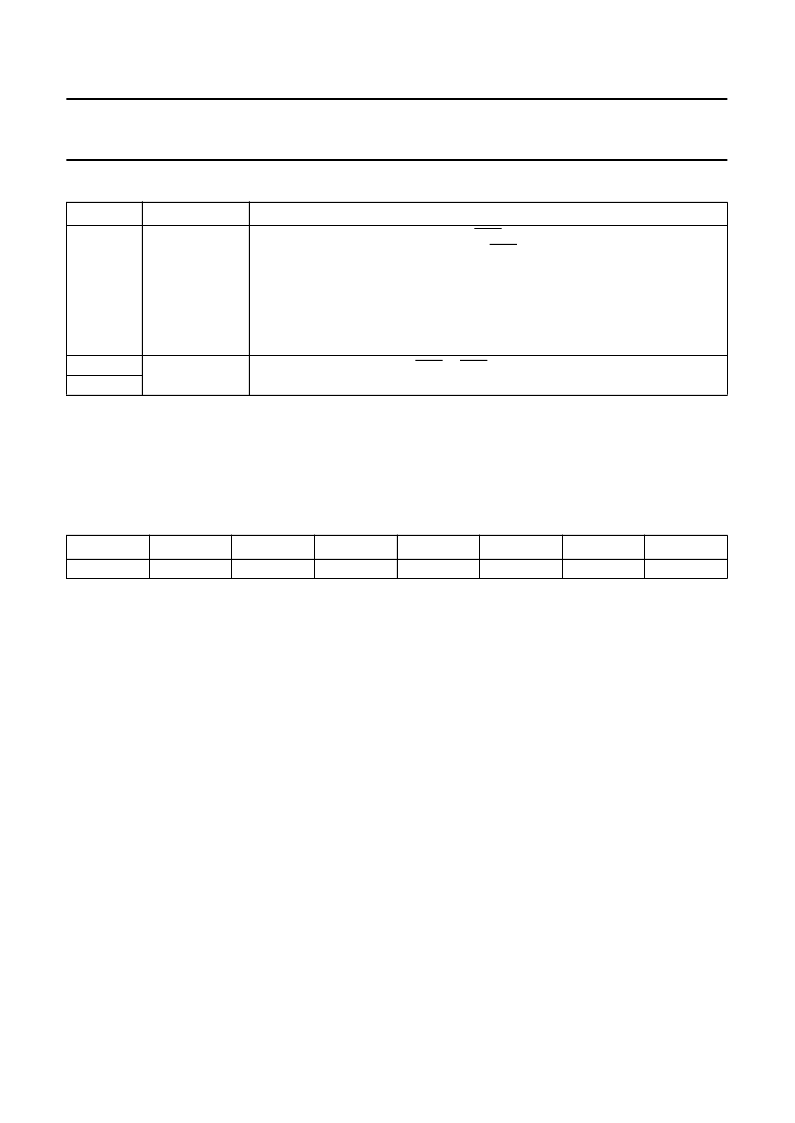

Table 19

Pending Interrupt Flag Register (address FFFF 810F)

BIT

SYMBOL

DESCRIPTION

7 and 3

PIRn

Pending interrupt request

. n = 0 to 7; INT7 corresponds to the interrupt NMIN;

PIRn = 1, pending interrupt request for pin INTn. PIRn = 0 (default value after a CPU

reset), no pending interrupt. When a valid interrupt request has been detected this bit

is set. It is automatically reset by the interrupt acknowledge cycle from the CPU. It

can be reset by software by writing a logic 0, however writing a logic 1 has no effect

on the flag. To reset only one flag, a logic 0 should be written to the bit address and a

logic 1 to the other interrupt requests. The use of BCLR instruction should be

avoided (PIR7 is cleared when the pin NMIN is set HIGH)

6 to 4

2 to 0

IPLm.2 to IPLm.0

Interrupt priority level of pins INT0 to INT6 (fixed to ‘111B’ for NMIN in LIR3);

m = 0 to 6.

7

6

5

4

3

2

1

0

PIF7

PIF6

PIF5

PIF4

PIF3

PIF2

PIF1

PIF0

6.7.3

N

OTE ON SIMULTANEOUS INTERRUPTS

If an internal interrupt is immediately followed by an

external interrupt (i.e. both interrupts occurring within 12

clock cycles) and both these interrupts have the same

interrupt level, then the CPU might hang up during the

acknowledge cycle of the internal interrupt.

In the interrupt controller a flag WIN is set for each interrupt

as soon as the interrupt is activated and will be reset when

an interrupt of higher priority occurs or during the

acknowledge cycle. The WIN flag is used to determine

which PIR flag should be reset.

A conflict occurs if within the interval starting at the CPU

sampling of the first internal interrupt and ending at the

acknowledge cycle, a second external interrupt resets the

WIN flag of the first interrupt (external interrupts have

higher priority than internal).

When the CPU acknowledges the first internal interrupt the

auto-vector acknowledge signal cannot be asserted as its

WIN flag was reset, and the CPU hangs up.

This situation can be solved by using the bus time-out

counter controlled by the System Control Register

(SYSCON) with the bits WD and WDSC set. In the case of

hang-up an internal bus error condition will be asserted

after 16 clocks and the CPU will execute the exception

SPURIOUS INTERRUPT at vector 60H. In the exception

service routine the interrupt flags PIR should be polled to

detect which interrupts caused the conflict, the

corresponding PIR flags should be cleared by software

and a call to the interrupt routines executed.

相關PDF資料 |

PDF描述 |

|---|---|

| P93U422-35DC | x4 SRAM |

| P93U422-35DM | x4 SRAM |

| P93U422-35DMB | x4 SRAM |

| P93U422-35LC | x4 SRAM |

| P93U422-35LM | x4 SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| P-90-F | 制造商:Hozan Tool Industrial Co Ltd 功能描述: |

| P90PCT101PC | 制造商:PERFORMANCE/ 功能描述:90PCT101PC |

| P-910 | 制造商:Hozan Tool Industrial Co Ltd 功能描述: |

| P9-100001 | 制造商:OTTO Engineering Inc 功能描述:P9-111122 EX H20 |

| P9-100002 | 制造商:OTTO Engineering Inc 功能描述:P9-111129 EX. |

發布緊急采購,3分鐘左右您將得到回復。